Source Impedance and Analog Measurements

A commonly overlooked detail when measuring analog voltages with data acquisition hardware is the voltage source's output impedance. Subtle interactions between the voltage source and the T7's analog to digital converter (ADC) circuitry can result in erroneous readings in certain situations. This application note describes issues caused by voltage source impedance, and how to approach measurements to ensure the greatest accuracy. This application references the T7 hardware specifically, however the concepts defined within are also valid for other hardware such as the T4, U6, and UE9 devices.

Static Errors

ADC Input Bias Currents

The ADC hardware is comprised of multiple components used for signal conditioning and analog to digital conversion. Each component possesses some amount of leakage or bias currents which interact amongst the various components. The combined effect is a small bias current seen at the analog inputs. Bias currents are currents that naturally flow into or out of the inputs on the T7. Since bias currents are inherent to the ADC layer's operation, they cannot be eliminated.

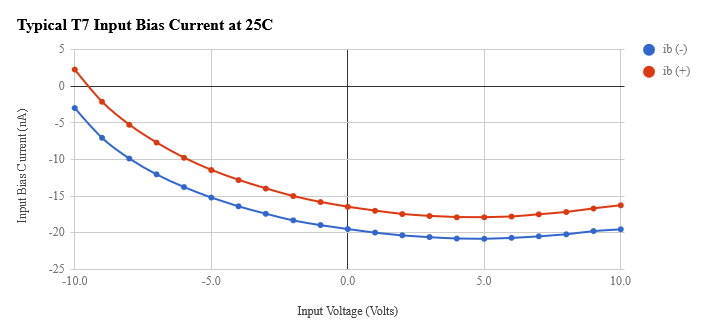

The magnitude of the bias currents are typically very small (nanoamps). The magnitude will vary to some degree, depending on the voltage applied to the analog inputs. The details behind bias current reaction with external voltages is complex. However, the overall affects are easily characterized using one of the two test setups shown in figure 1 and figure 2.

Figure 1 depicts a single-ended test which measures a known variable voltage source on AIN0 and AIN1. The difference between the voltage at the two inputs is due to the voltage drop across the resistor at AIN0, which is in turn used to calculate the bias current.

Figure 2 depicts a differential test which used for determining bias currents for the positive and negative inputs on a differential input. The differential measurement on the AIN0-1 pair is subtracted from the differential reading on AIN2-3. The difference between the two readings is due to the bias current flowing through the input resistor on AIN0. Note that only one resistor is used at any time, and the calculated bias current only apply to the input the resistor is on.

Figure 3 depicts typical bias currents for then T7s positive and negative inputs. The depicted bias current was collected using the differential test setup shown in figure 2. The single ended case will perform identically to the positive input case since the positive input and single-ended input circuits are identical. Bias current data was collected at 25C to apply to most applications. Bias currents are dependent on operating temperature. It is left to the user to determine bias current effects at operating temperatures other than what is shown.

Static Offsets

In practice, bias current show up as voltage offsets across the voltage signal's source resistance. The error between measured and actual can be either positive or negative depending on the bias current direction. Figures 4 and 5 depict how bias currents interact with source resistances in single-ended and differential measurements. Note that the positive direction for current flow is defined as flowing into the T7's inputs.

Weather or not the bias currents need to be dealt with will ultimately depend on source resistance and accuracy requirements. Single-ended measurement are the easiest to deal with because the static error is simply the expected bias current multiplied by the source resistance. Differential measurements can be more involved, and the end-effects will depend greatly on the source topology. Characterization of differential configurations is beyond the scope of this application note, and it is left to the user to test their hardware to determine bias current effects.

Dynamic Errors

Analog Input Dynamic Response

Dynamic errors are erroneous voltage readings caused by the input channel's dynamic response when the hardware switches between input channels. There are two main components which dictate the input channels dynamic response:

-

Source Impedance

-

Input Impedance

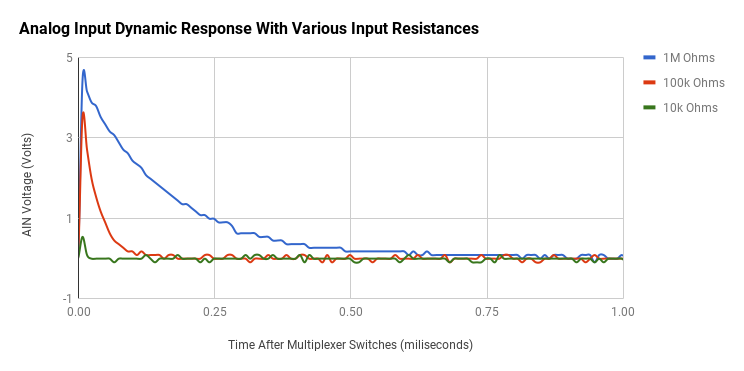

An input's dynamic response comes into play when the multiplexer switches between channels. For example, assume a situation where an analog reading just completed on AIN0 when the multiplexer switches to AIN1 to make a new conversion. The input circuitry is still at the voltage from the previous analog reading after the multiplexer switches (voltage on AIN0). The residual voltage on the input circuitry must charge/discharge to equilibrium with the current input voltage. The charging/discharging characteristics depends on the combined source and channel impedance. The input signal will generally follow some decay or damped oscillation due to the input's combined impedance. The exact charge/discharge shape is not a concern. The important concept is the time required for the input signal to come to equilibrium after the multiplexer switches. The amount of time required for the input to come to equilibrium is dominated by the source resistance and voltage differential between successive analog reading on different channel. Figure 7 depicts typical decay profiles on an analog input with connected to ground through different resistances.

The data in figure 7 was collected from an analog input signal immediately after sampling from a different channel connected to a 10V DC signal. Figure 8 depicts a simple test setup to measure input channel dynamic response, using an oscilloscope to collect waveform data.

Settling Time

Erroneous voltage readings occur when a ADC conversion occurs before a channel's dynamic characteristics have had a chance to decay to accuracy levels. A short delay is introduced in firmware after the multiplexer switches to prevent such errors from being introduced into analog readings. This short delay is called settling time and is directly accessible through AINn_SETTLING_US parameter. The settling time may be individually set for each input channel where valid values range are 0-50,000. A settling time value of 0 is reserved for the default settling times (Table 1) and 1-50,000 user defined settling times defined in microseconds. Table 1 lists the auto settling times (AINn_SETTLING_US = 0) which are suggested for source resistances up to 1k Ohms.

|

Gain |

Res Index |

Auto Settling |

|---|---|---|

|

[us] |

||

|

1 |

1 |

10 |

|

4 |

10 |

|

|

8 |

10 |

|

|

9 |

10 |

|

|

12 |

10 |

|

|

10 |

1 |

200 |

|

4 |

500 |

|

|

8 |

2000 |

|

|

9 |

10 |

|

|

12 |

10 |

|

|

100 |

1 |

1000 |

|

4 |

5000 |

|

|

8 |

10000 |

|

|

9 |

10 |

|

|

12 |

10 |

|

|

1000 |

1 |

5000 |

|

4 |

5000 |

|

|

8 |

10000 |

|

|

9 |

10 |

|

|

12 |

10 |

Table 1: Auto settling times for various range and resolution index settings. Auto settling times are adequate for source resistance up to 1k Ohms.

Table 2 lists suggested settling times for source resistances between 1k Ohms and 1M Ohms. The values listed in the table are suggested values to use as a starting point. Note that auto settling times are adequate for source resistances in excess of 1k Ohms.

|

Gain |

Res Index |

Source Resistance [Ohms] |

|||

|---|---|---|---|---|---|

|

1k |

10k |

100k |

1M |

||

|

1 |

1 |

Auto |

Auto |

100 |

5k |

|

4 |

Auto |

Auto |

500 |

250k |

|

|

8 |

Auto |

Auto |

Auto |

OS |

|

|

9 |

Auto |

Auto |

Auto |

OS |

|

|

12 |

Auto |

Auto |

Auto |

Auto |

|

|

10 |

1 |

Auto |

1k |

5k |

OS |

|

4 |

Auto |

Auto |

10k |

1M |

|

|

8 |

Auto |

Auto |

OS |

OS |

|

|

9 |

Auto |

Auto |

OS |

OS |

|

|

12 |

Auto |

Auto |

Auto |

750k |

|

|

100 |

1 |

Auto |

OS |

OS |

OS |

|

4 |

Auto |

OS |

OS |

OS |

|

|

8 |

Auto |

OS |

OS |

OS |

|

|

9 |

Auto |

OS |

OS |

OS |

|

|

12 |

Auto |

Auto |

500k |

OS |

|

|

1000 |

1 |

Auto |

OS |

OS |

OS |

|

4 |

Auto |

OS |

OS |

OS |

|

|

8 |

Auto |

OS |

OS |

OS |

|

|

9 |

Auto |

OS |

OS |

OS |

|

|

12 |

Auto |

Auto |

1M |

OS |

|

Table 2: Suggested settling times for various source resistances [us].

[1.] Settling times are listed in microseconds.

[2.] OS indicates analog readings did not meet absolute accuracy specifications, using settling times of one second. Additional settling time may be required to achieve desired accuracy.

In certain applications, settling times greater than 50 milliseconds may be required to achieve desired accuracy. To accommodate these situations the settling time must be implemented in software. Software implemented settling times are created by taking two consecutive readings on the same channel, separated by some specified delay in software. The first reading is used two switch the multiplexer to the desired channel only, and is simply ignored. Next, the software delay for a specified amount of time, allowing the input's dynamic characteristics diminish, achieving full accuracy. A second analog reading is taken immediately after the delay, resulting in a valid reading.

T7 Sampling Details

When the stream scan goes to acquire a channel, it sets the muxes to connect the channel to the internal in-amp (this actually happens near the start of the last ADC conversion period of the previous channel), then waits the specified settling time, then acquires 1 or more samples from the ADC. For each sample the ADC sampling cap is connected for only 1 us (ADC acquisition time), then ADC conversion time is about 3.2 us. The "1 or more samples" part has to do with ResolutionIndex which does oversampling & averaging where ResolutionIndex=1 corresponds to 1 sample, ResolutionIndex=2 corresponds to 2 samples, ResolutionIndex=4 corresponds to 4 samples, and so on up to ResolutionIndex=8 which corresponds to 128 samples.

Settling Tests

Settling errors arise when signals have weak drive (aka high source impedance). Here are some tests to check signals for weak drive. The following tests are described for a T7 using LJStreamM, but similar tests apply to other devices.

The following tests are done on a T7 analog input using the ±10 volt range where the specified accuracy is 2 mV, so errors (changes) greater than 2 mV are what we are looking for.

Connect the signal in question to AIN0. Jumper AIN2 to GND and AIN3 to VS.

Use LJStreamM with ScanRate=100 for all of these tests.

A: Set #Channels=1 and in the first row set Name=AIN0. The voltage displayed in the first row is the command-response reading from AIN0. Click StartStream, and now the voltage displayed in the first row is the average of the stream readings from AIN0. Even weaker signals will do good in this test, as the multiplexer is not changing and thus no settling is needed.

B: Click StopStream, set #Channels=6, in the first row set Name=AIN3, in the next 5 rows set Name=AIN0, and click StartStream. If the signal settles properly the first reading of it (2nd row) will be correct and all 5 readings will be about the same.

C: Click StopStream, set #Channels=4, set the names to AIN3, AIN0, AIN2, AIN0, and click StartStream. The first reading of AIN0 has to settle from 5 volts, while the second reading of AIN0 has to settle from 0 volts, so if both readings of AIN0 agree the signal is settling properly from 2 different starting points.

For any of these tests, to simulate a high impedance signal and see settling problems you can use GND or some other signal with a resistor in series.

In test B, if settling problems are observed you can try increasing STREAM_SETTLING_US. This is not controllable from LJStreamM, so close LJStreamM, use the Register Matrix in Kipling, close Kipling, and then run LJStreamM again. Note that you will get a scan overlap error if NumChannels*SettlingTime exceeds the scan interval.

Channel Crosstalk

Channel crosstalk is a condition where a time-varying signal on one channel is imposed onto an adjacent channel due to pure electric coupling. Channel crosstalk is often confused with the dynamic errors described above. Extensive design efforts are taken to eliminate channel crosstalk to where it is not an issue. Please refer to appendix A-3 in the T7 datasheet to review the channel crosstalk specification.